Advanced Science And Novel Technology Company, Inc. 2790 Skypark Drive Suite 112, Torrance, CA 90505

> Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

## ASNT\_501 2kHz-41GHz Clock Divide-by-8/2-to-1024

- Broadband frequency range from 2kHz 41GHz

- Minimal insertion jitter

- Fast rise/fall times

- 50% duty cycle for all divide ratios

- Selectable divide output up to 1024

- Second divide by 8 output

- Positive +3.3*V* supply

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

## DESCRIPTION

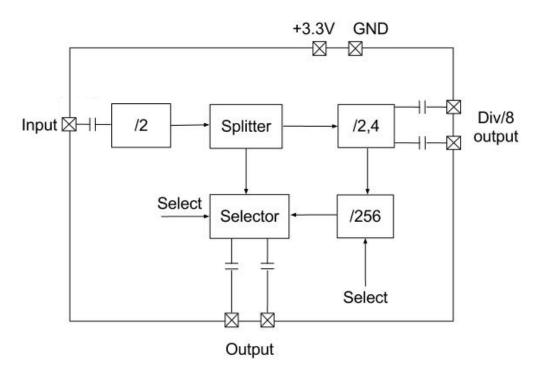

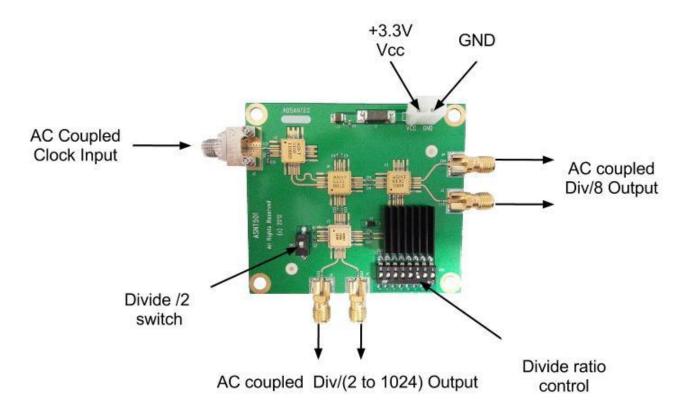

Fig. 1 Functional Block Diagram

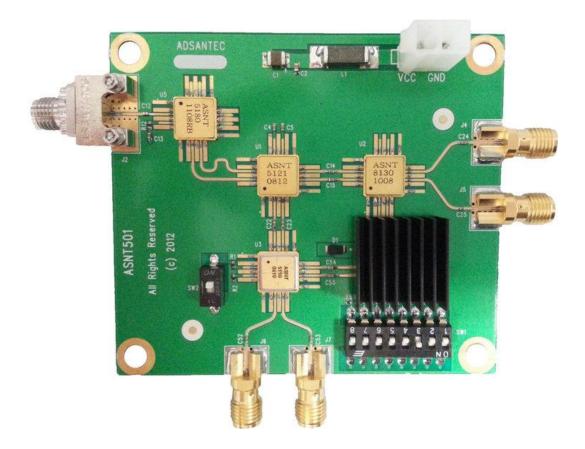

The ASNT\_501 system on board functions as a multi-purpose divider for test, microwave, and communication applications. The selectable divide output can be operated single-ended or differentially. A secondary fixed divide-by-8 output can also be used single-ended or differentially. The high-speed clock input is AC coupled with a K-type Southwest connector MFG PN: 1092-03A-5. The clock outputs are AC coupled with Emerson SMA connectors MFG PN: 142-0761-881. Power is supplied through a two pin MOLEX connector P/N: 39-28-1023.

### **APPLICATIONS**

The ASNT\_501 divider can be used as a prescaler to extend the useful frequency range for triggering. The second fixed **divide-by-8** output can be used to synchronize other devices. The divider can also be used as a prescaler for PLL's or frequency counters.

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

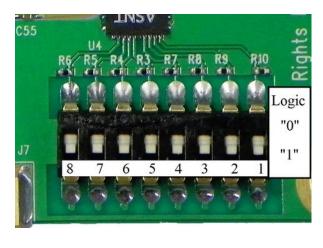

#### **DIVIDE RATIO CONTROL**

The divide by (2-to-1024) output has been configured to divide the input frequency ratio from 2 to 1024. The following equation {Div/ output n = 4m}, where m is an integer from 1 to 256 which provides all possible divide ratios. The divide ratio control contains 8 switches which represent 8 bits. The LSB starts at SW1 and the MSB ends at SW8. The binary value of zero gives a decimal m value of 256. Ascending binary values increase the decimal value m. Table 1 shows values of m with their corresponding binary representation.

| Table 1. Binary Values for Divide Ratio |              |                     |  |  |

|-----------------------------------------|--------------|---------------------|--|--|

| DIP SW #                                | m            | n                   |  |  |

| 37654321                                | Switch Ratio | <b>Divide Ratio</b> |  |  |

| ) 0 0 0 0 0 0 1                         | 1            | 1                   |  |  |

| DII BW #  |              | 11                  |

|-----------|--------------|---------------------|

| 87654321  | Switch Ratio | <b>Divide Ratio</b> |

| 00000001  | 1            | 4                   |

| 0000010   | 2            | 8                   |

| 0000011   | 3            | 12                  |

| 00000100  | 4            | 16                  |

| •••       |              |                     |

| 00011001  | 25           | 100                 |

| •         |              |                     |

| •         |              |                     |

| •         |              |                     |

| 11111010  | 250          | 1000                |

| •••       |              |                     |

| 11111111  | 255          | 1020                |

| 000000000 | 256          | 1024                |

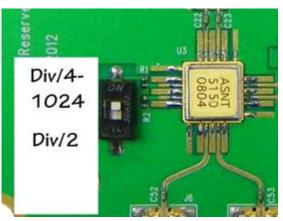

#### **DIVIDE-BY-2 SWITCH**

Switching the divide-by-2 switch to the position shown below (Div/2) will override any divide ratio that is currently set on the divide ratio control and output a divide-by-2. Switching the divide-by-2 switch to the position below (Div/4-1024) will turn on the divide ratio control.

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

## ABSOLUTE MAXIMUM RATINGS

Caution: Exceeding the absolute maximum ratings shown in <u>Table 2</u> may cause damage to this product and/or lead to reduced reliability. Functional performance is specified over the recommended operating conditions for power supply and temperature only. AC and DC device characteristics at or beyond the absolute maximum ratings are not assumed or implied. All min and max voltage limits are referenced to ground.

| Parameter                   | Min | Max  | Units |

|-----------------------------|-----|------|-------|

| Supply Voltage (vee)        |     | +3.6 | V     |

| Power Consumption           |     | 3.6  | W     |

| RF Input Voltage Swing (SE) |     | 1.0  | V     |

| Case Temperature            |     | +90  | °С    |

| Storage Temperature         | -40 | +100 | °С    |

| Operational Humidity        | 10  | 98   | %     |

| Storage Humidity            | 10  | 98   | %     |

|  | Table 2. | Absolute | Maximum | Ratings |

|--|----------|----------|---------|---------|

|--|----------|----------|---------|---------|

### **TERMINAL FUNCTIONS**

Advanced Science And Novel Technology Company, Inc. 2790 Skypark Drive Suite 112, Torrance, CA 90505

Ultra High-Speed Mixed Signal ASICs

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

# **ELECTRICAL CHARACTERISTICS**

| PARAMETER                | MIN                  | TYP               | MAX                 | UNIT             | COMMENTS                 |

|--------------------------|----------------------|-------------------|---------------------|------------------|--------------------------|

| General Parameters       |                      |                   |                     |                  |                          |

| V <sub>EE</sub>          |                      | 0                 |                     | V                | External ground          |

| V <sub>CC</sub>          | 3.1                  | 3.3               | 3.5                 | V                |                          |

| Ivcc                     |                      | 1100              |                     | mА               |                          |

| Power                    |                      | 3.6               |                     | W                |                          |

| Operating<br>Temperature | -25                  | 50                | 85                  | °C               |                          |

|                          |                      | Clo               | ck Input            |                  |                          |

| Frequency                | 2.0E-5               |                   | 41                  | GHz              |                          |

| Single-ended Swing       | 50                   | 400               | 1000                | mV <sub>PP</sub> |                          |

| Common Mode<br>Level     | V <sub>CC</sub> -0.8 | V <sub>CC</sub> - | 0.2 V <sub>CC</sub> | V                |                          |

| Duty Cycle               | 40                   | 50                | 60                  | %                | Range of input tolerance |

|                          |                      | Outp              | ut ( <b>Div/8</b> ) |                  |                          |

| Frequency                | 2.0E-5               |                   | 5.125               | GHz              |                          |

| Single-ended Swing       | 380                  | 400               | 420                 | mV <sub>PP</sub> |                          |

| Rise/Fall Time           | 10                   | 12                | 14                  | ps               | 20% to 80%               |

| Additive Jitter          |                      | <1                |                     | ps               | Peak-to-Peak             |

| Duty Cycle               | 45                   | 50                | 55                  | %                | For clock signal         |

| Output (2-to-1024)       |                      |                   |                     |                  |                          |

| Frequency                | 2.0E-5               |                   | 20.5                | GHz              |                          |

| Single-ended Swing       | 380                  | 400               | 420                 | mV <sub>PP</sub> |                          |

| Rise/Fall Time           | 10                   | 12                | 14                  | ps               | 20% to 80%               |

| Additive Jitter          |                      | <1                |                     | ps               | Peak-to-Peak             |

| Duty Cycle               | 45                   | 50                | 55                  | %                | For clock signal         |

Ultra High-Speed Mixed Signal ASICs

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

# **REVISION HISTORY**

| Revision      | Date    | Changes                                 |  |  |

|---------------|---------|-----------------------------------------|--|--|

| 1.6.2         | 07-2019 | Updated Letterhead                      |  |  |

| 1.6.1         | 04-2019 | Reverted Previous Change                |  |  |

|               |         | Added P/N to connectors' description    |  |  |

| 1.5.1         | 07-2018 | Updated Input Connector to SV Microwave |  |  |

| 1 / 1         | 09-2015 | Corrected Power Consumption Information |  |  |

| 1.4.1 09-2015 |         | Corrected Divide-by-2/4-1024 Picture    |  |  |

|               |         | Revised title                           |  |  |

| 1.3.1         | 05-2013 | Revised description                     |  |  |

| 1.3.1         |         | Revised applications                    |  |  |

|               |         | Revised divide ratio control            |  |  |

|               |         | Updated maximum operating frequency     |  |  |

| 1.2.1 03-2013 | 03 2013 | Updated functional block                |  |  |

|               | 03-2013 | Updated format                          |  |  |

|               |         | Added maximum ratings                   |  |  |

| 1.1.1 03-20   | 03 2013 | Updated pictures                        |  |  |

|               | 03-2013 | Update PN for connectors                |  |  |

| 1.0.1         | 07-2012 | Revised formatting                      |  |  |

| 1.0           | 04-2012 | Initial release                         |  |  |